# **15-CHARACTER 1-LINE DOT MATRIX LCD** CONTROLLER DRIVER with OUTPUT PORT

#### ■ GENERAL DESCRIPTION

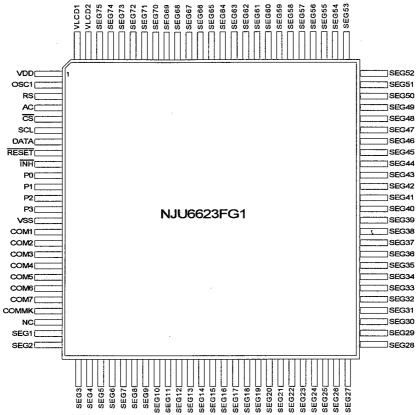

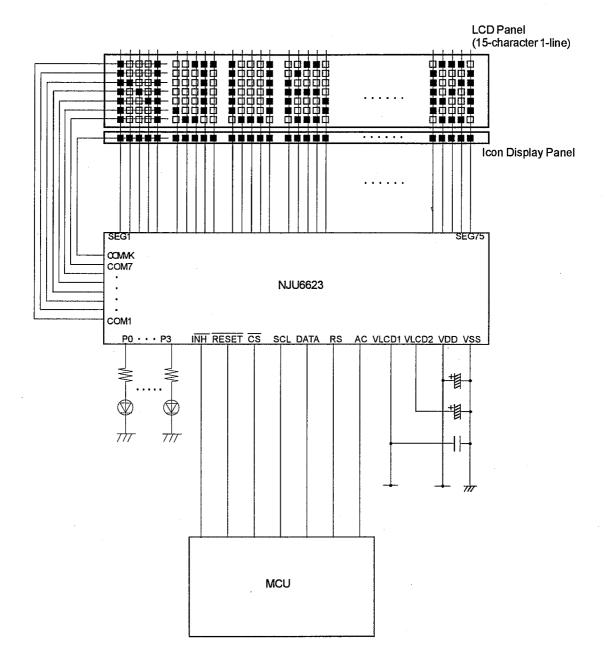

The NJU6623 is a Dot Matrix LCD controller driver for 15-character 1line with icon display in single chip.

It contains bleeder resistance, general output port, CR oscillator, microprocessor interface circuits, instruction decoder controller, character generator ROM/RAM, high voltage operation common and segment drivers.

The character generator ROM consists of 7,840 bits stores 224 kinds of character Font. Each 1,120 bits CG RAM and Icon display RAM can stores 32 kinds of special character displayed on the dot matrix display area or 75 kind of Icon on the Icon display area.

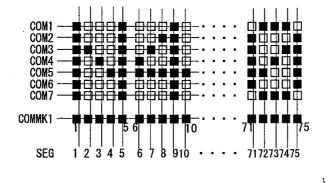

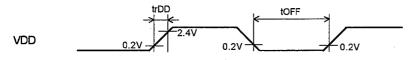

The 8-common (7 for character, 1 for icon) and 75-segment drivers operated 15-character 1-line with 75 Icon LCD display and LED driver drives 4 LED which can use like as indicator.

The 16th grav scale contrast control function is incorporated for its adjustment. Therefore, simple power supply circuit and easy contrast adjustment are available.

The complete CR oscillator is incorporated, therefore no external components for oscillation circuit are required.

The microprocessor interface circuits which operate by 1MHz, can be selected serial interface.

# **FEATURES**

- 15-character 1-line Dot Matrix LCD Controller Driver

- Maximum 75 Icon Display

- Serial Direct Interface with Microprocessor

- Display Data RAM - 15 x 8 bits : Maximum 15-character 1-line Display

- 7,840 bits : 224 Characters for 5 x 7 Dots Character Generator ROM

- Character Generator RAM 1,120 bits : 32 Patterns( 5 x 7 Dots ) - 15 x 5 bits : Maximum 75 Icons

- Icon Display RAM High Voltage LCD Driver

- : 8-common / 75-seament

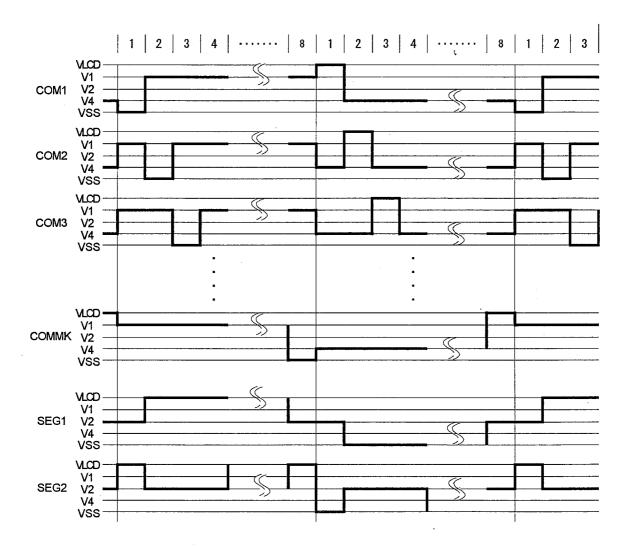

- Duty and Bias Ratio : 1/8 duty, 1/4 bias

- Useful Instruction Set

- : Clear Display, Address Home, Display ON/OFF Cont, Display Blink, Address Shift, Character Shift

- General output port (4 ports)

- Power On Initialization / Hardware Reset

- Bleeder Resistance on-chip

- Software contrast control(16 step)

- Oscillation Circuit on-chip

- Low Power Consumption

- Operating Voltage --- 2.4 to 5.5 V

- Package Outline --- QFP 100

- C-MOS Technology

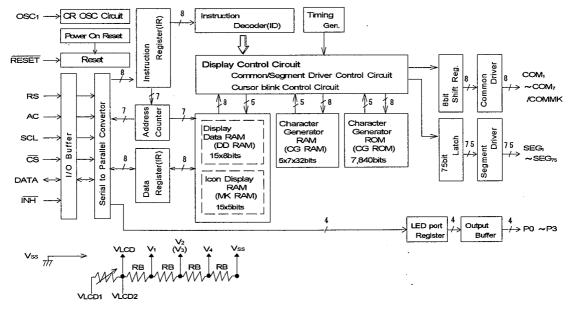

■PACKAGE OUTLINE

NJU6623 PRELIMINARY

NJU6623FG1

Mar. 1999 Ver.3

New Japan Radio Co., Ltd.

#### **PINCONFIGURATION**

# BLOCK DIAGRAM

# ■ TERMINAL DESCRIPTION

| No.   | SYMBOL     | 1/0 | FUNCTION                                                                                                                      |

|-------|------------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 1,14  | VDD,VSS    | -   | Power Source:VDD=+5V,GND:VSS=0V                                                                                               |

| 100   | VLCD1      | ł   | LCD driving voltage input terminal                                                                                            |

| 99    | VLCD2      | I   | LCD driving voltage stabilize capacitor terminal<br>connect the capacitor between VLCD2 and VSS<br>typ. : 0.1uF               |

| 2     | OSC1       | i   | System clock input terminal<br>This terminal should be open for internal clock operation.                                     |

| 3     | RS         | I   | Register selection signal input terminal<br>"0":Instruction register<br>"1":Data register                                     |

| 4     | AC         | I   | Set CG RAM address selection signal input terminal<br>"0":other Instruction<br>"1":Set CG RAM Address                         |

| 5     | CS         | I   | Chip select signal input in serial mode                                                                                       |

| 6     | SCL        | I   | Sift clock input in serial mode                                                                                               |

| 7     | DATA       | I   | Serial Data Input terminal                                                                                                    |

| 8     | RESET      | ł   | Reset Terminal.<br>When the "L" level input over than 1.2ms to this terminal,<br>the system will be reset ( at fosc 153KHz ). |

| 9     | ĪNĦ        | I   | Stand-by mode terminal<br>When the "L" level input to this terminal,<br>the system will be low power mode(stand-by mode).     |

| 10-13 | P0-P3      | 0   | General output port<br>LED driver drives LED which can use like as indicator.                                                 |

| 15-21 | COM1-COM7  | 0   | LCD common driving signal output terminals                                                                                    |

| 22    | СОММК      | 0   | Icon common driving signal output terminals                                                                                   |

| 24-98 | SEG1-SEG75 | 0   | LCD segment driving signal output terminals                                                                                   |

| 23    | NC         |     | These terminals are electrically open.                                                                                        |

#### ■ FUNCTIONAL DESCRIPTION

(1-1)Register

The NJU6623 incorporates two 8-bit registers, an Instruction Register(IR) and a Data Register(DR). The Register(IR) stores instruction codes such as "Clear Display" and "Cursor Shift" or address data for Display Data RAM(DD RAM), Character Generator RAM(CG RAM) and Icon Display RAM (MK RAM).

The Register(DR) is a temporary stored register, the data stored in the Register(DR) is written into the DD RAM, CG RAM or MK RAM.

The data in the Register(DR) written by the MPU is transferred automatically to the DD RAM, CG RAM or MK RAM by internal operation.

These two registers are selected by the selection signal RS as shown below.

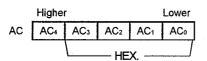

#### (1-2)Address Counter (AC)

The address counter(AC) addresses the DD RAM, CG RAM or MK RAM.

When the address setting instruction is written into the Register(IR), the address information is transferred from Register(IR) to the Counter(AC). The selection of either the DD RAM, CG RAM or MK RAM is also determined by this instruction.

After writing (or reading) the display data to (or from) the DD RAM, CG RAM or MK RAM, the Counter(AC) increments (or decrements) automatically.

#### (1-3) Display Data RAM (DD RAM)

The display data RAM (DD RAM) consists of 15 x 8 bits stores up to 15-character display data represented in 8bit code.

The DD RAM address data set in the address counter(AC) is represented in Hexadecimal.

(Example) DD RAM address " 08 "

| 0 | 1 | 0 | 0 | 0 |

|---|---|---|---|---|

|   |   |   |   |   |

The relation between DD RAM address and display position on the LCD is shown below.

| 1  | 2  | 3  | 4  | 5  | 6 · | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | -Display Position      |

|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|------------------------|

| 00 | 01 | 02 | 03 | 04 | 05  | 06 | 07 | 08 | 09 | 0A | 0B | 0Ċ | 0D | 0E | -DD RAM Address (Hex.) |

When the display shift is performed, the DD RAM address changes as follows:

(Left Shift Display)

|        | •    |        |        |       |    |    |    |    |    |    |    |    |    |    |    |        |

|--------|------|--------|--------|-------|----|----|----|----|----|----|----|----|----|----|----|--------|

| (00)<= | 01   | 02     | 03     | 04    | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 00 |        |

|        | (Rig | iht Sł | nift D | ispla | () |    |    |    |    |    |    |    |    |    |    |        |

|        | 0E   | 00     | 01     | 02    | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | =>(0E) |

(1-4)Character Generator ROM (CG ROM)

The Character Generator ROM (CG ROM) generates 5 x 7 dots character pattern represented in 8-bit character code.

The storage capacity is up to 224 kinds of 5 x 7 dots character pattern(available address is (20)<sub>H</sub> through (FF)<sub>H</sub>). The correspondence between character code and standard character pattern of NJU6623 is shown in Table 2. User-defined character patterns (Custom Font) are also available by mask option.

New Japan Radio Co., Ltd.

|                  |    |                   |      |        |       |   |      | Upp         | er 4bi | (HEX     | .)            |            |      | -    |     |            |                                        |

|------------------|----|-------------------|------|--------|-------|---|------|-------------|--------|----------|---------------|------------|------|------|-----|------------|----------------------------------------|

|                  |    | 0                 | 1    | 2      | 3     | 4 | 5    | 6           | 7      | 8        | .9            | A          | В    | С    | D   | E          | F                                      |

|                  | 0  | CG<br>RAM<br>(01) | (17) |        |       |   |      | •           | ÷      | <b>.</b> |               |            |      |      |     |            |                                        |

|                  | 1  | (02)              | (18) | :      |       |   |      |             | ·::::  |          |               |            |      |      | ;;  |            | 4                                      |

|                  | 2  | (03)              | (19) | ::     | ·     |   |      |             |        |          |               |            | •    |      |     | <u>.</u> : |                                        |

|                  | 3  | (04)              | (20) |        | ••    |   | ::   | : <u></u> . | ::::·  |          |               |            |      |      | 1   | :          | ::-: <b>:</b>                          |

|                  | 4  | (05)              | (21) |        | ::    |   |      |             | ·      |          |               | •••        |      | ÷    | 17  | <b>.</b> 1 |                                        |

|                  | 5  | (06)              | (22) |        |       |   |      | ::::·       | ii     |          |               | ::         |      |      |     |            |                                        |

|                  | 6  | (07)              | (23) |        |       |   |      | ÷           | ÷.,.÷  |          |               |            | 17   | •••• |     | ÷          | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |

| (HEX.)           | 7  | (08)              | (24) |        |       |   |      |             |        | ÷::      |               |            |      |      |     |            |                                        |

| Lower 4bit(HEX.) | 8  | (09)              | (25) |        |       |   |      |             | :::    | <u>.</u> | •             | ·:         |      |      |     |            |                                        |

|                  | 9  | (10)              | (26) | •••••• |       |   |      | 1           | ·!     |          |               | -          | · ]] | •    |     | ·· :       | ·                                      |

|                  | A  | (11)              | (27) | :::::  | ::    |   |      |             |        |          |               |            |      |      | ·   |            | :::::                                  |

|                  | В  | (12)              | (28) | ·      | ::    |   |      | :           |        | ï        | : <b>:</b> :. |            | Ţ    |      |     | ∷          |                                        |

|                  | С  | (13)              | (29) | :      | •••   |   | ÷    |             |        | İ        | <u>.</u>      | <u>;;;</u> | :    |      |     | :          |                                        |

|                  | D  | (14)              | (30) |        |       |   |      |             |        |          |               |            |      | ··   |     | ÷          |                                        |

|                  | E  | (15)              | (31) | ::     | ••••• |   | ···· |             | ·-::-  |          |               |            | 1    | :::: | ••• |            |                                        |

|                  | F. | (16)              | (32) |        |       |   |      | :           | ÷      |          |               | • ::•      | ·    | ~;   | ::: |            |                                        |

Table 2. CG ROM Character Pattern (ROM version -02)

New Japan Radio Co., Ltd.

.

#### (1-5)Character Generator RAM (CG RAM)

The character generator RAM ( CG RAM ) can store any kind of character pattern in 5 x 7 dots written by the user program to display user's original character pattern. The CG RAM can store 32 kind of character in 5 x 7 dots mode.

To display user's original character pattern stored in the CG RAM, the address data (00)+-(1F)+ should be written to the DD RAM as shown in Table 2.

Table 3. show the correspondence among the character pattern, CG RAM address and Data.

| Character Code<br>(DD RAM Data) | CG RAM Address                                                                 | Character<br>Pattern<br>(CG RAM Data)     |                                                       |

|---------------------------------|--------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------|

| 76543210                        | 76543210                                                                       | $\leftarrow \overset{43210}{\rightarrow}$ |                                                       |

| Upperbit Lowerbit               | Upperbit Lowerbit                                                              | Upper Lower<br>bit bit                    |                                                       |

| 00000000                        | 0 0 0 0<br>0 0 1<br>0 0 0 0 0<br>0 0 0 0 0<br>1 0 1<br>1 0 0<br>1 1 1<br>1 1 1 |                                           | Character Pattern<br>Example(1)<br><= Cursor Position |

| 00000001                        | 0000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                          |                                           | Character Pattern<br>Example(2)<br><= Cursor Position |

|                                 | 000<br>001                                                                     |                                           |                                                       |

|                                 |                                                                                | •<br>•<br>•                               |                                                       |

| •                               | · · ·                                                                          |                                           |                                                       |

| 00011111                        | 11111                                                                          |                                           | *=Don't care                                          |

|                                 | 100<br>101<br>110<br>111                                                       |                                           |                                                       |

Table 3. Correspondence of CG RAM address, DD RAM character code and CG RAM character pattern( 5 x 7 dots )

Notes :

- 1. Character code bit 0 to 4 correspond to the CG RAM address bit 3 to 7(5bits:32 patterns).

- 2. CG RAM address 0 to 2 designate character pattern line position. The 8th line is Don't care line. In case of input CG RAM data continuously, invalid address are Cursor position automatically.

- 3. Character pattern row position correspond to the CG RAM data bits 0 to 4 are shown above.

- 4. CG RAM character patterns are selected when character code of DD RAM bits 5 to 7 are all "0" and these are addressed by character code bits 0 and 1.

- 5. "1" for CG RAM data corresponds to display On and "0" to display Off.

#### (1-6)Icon Display RAM (MK RAM)

The NJU6623 can display maximum 75 lcons.

The lcon Display can be controlled by writing the Data in MK RAM corresponds to the lcon. The relation between MK RAM address and lcon Display position is shown below:

Table 4. Correspondence among Icon Position, MK RAM Address and Data

| MK RAM Add | dress     | Bits for Icon Display Position |   |    |      |      |      |      |      |  |  |  |

|------------|-----------|--------------------------------|---|----|------|------|------|------|------|--|--|--|

| (10н-1Ен)  | (10н-1Ен) |                                |   | D₅ | D₄   | D3   | D2   | D1   | D₀   |  |  |  |

| 1 0000     | 10н       | 0                              | 0 | 0  | "1"  | "2"  | "3"  | "4"  | "5"  |  |  |  |

| 1 0001     | 11н       | 0                              | 0 | 0  | "5"  | "7"  | "8"  | "9"  | "10" |  |  |  |

| 1 0010     | 12н       | 0                              | 0 | 0  | "11" | "12" | "13" | "14" | "15" |  |  |  |

| 1 0011     | 13н       | 0                              | 0 | 0  | "16" | "17" | "18" | "19" | "20" |  |  |  |

| :          | :         |                                |   |    |      | :    |      |      |      |  |  |  |

| 1 1110     | 1Ен       | 0                              | 0 | 0  | "71" | "72" | "73" | "74" | "75" |  |  |  |

Notes : When the Icon display function using, the system should be initialized by the software initialization because the MK RAM is not initialized by the power turning on and hardware reset.

#### (1-7) Timing Generator

The timing generator generates a timing signals for the DD RAM, CG RAM and MK RAM and other internal circuits.

RAM read timing for the display and internal operation timing for MPU access are separately generated, so that they may not interfere with each other.

Therefore, when the data write to the DD RAM for example, there will be no undesirable influence, such as flickering, in areas other than the display area.

#### (1-8)LCD Driver

LCD Driver consists of 8-common driver and 75-segment driver.

The character pattern data are latched to the addressed Segment-register respectively. This latched data controls display driver to output LCD driving waveform.

New Japan Radio Co., Ltd.

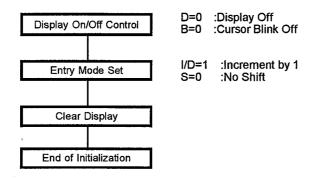

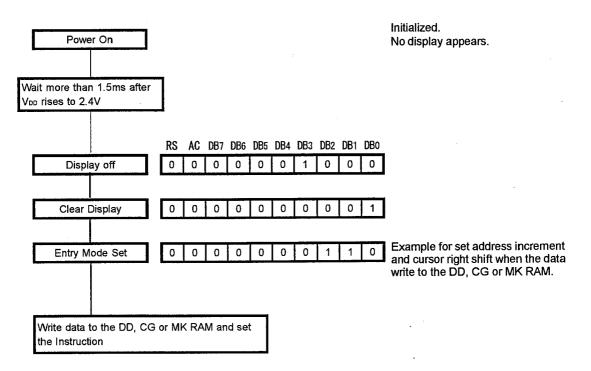

(2) Power on Initialization by internal circuits

(2-1)Initialization By Internal Reset Circuits

The NJU6623 is automatically initialized by internal power on initialization circuits when the power is turned on. In the internal power on initialization, following instructions are executed. During the Internal power on initialization, the busy flag (BF) is "1" and this status is kept 1.5ms (fosc=153kHz) after V<sub>DD</sub> rises to 2.4V. Initialization flow is shown below:

Note : If the condition of power supply rise time described in the Electrical Characteristics is not satisfied, the internal Power On Initialization Circuits will not operated and initialization will not performed. In this case the initialization by MPU software is required.

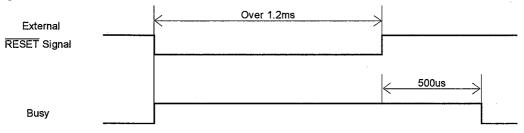

#### (2-2)Initialization By Hardware

The NJU6623 incorporates RESET terminal to initialize the all system. When the "L" level input over 1.2ms to the RESET terminal, reset sequence is executed. In this time, busy signal output during 500us (fosc=153kHz) after RESET terminal goes to "H". During this 500us period, any other instruction must not be input to the NJU6623.

-Timing Chart

#### (3)Stand by Mode

The NJU6623 equipped stand by mode for reducing power consumption. Setting of stand by mode are INH terminal = "L", return to stand by mode are INH terminal = "H". The internal circuit of stand by mode shown below,

-All character, mark off.

-The contents of written data for DD/CG/MK RAM will be hold.

-Osc circuit will be stop, COM,SEG output terminal VLCD level.

Note) In case of stand by mode, it should not be input a instruction, it will be come error factor.

# (4)Instructions

The NJU6623 incorporates two registers, an Instruction Register (IR) and a Data Register(DR).

These two registers store control information temporarily to allow interface between NJU6623 and MPU or peripheral ICs operating different cycles. The operation of NJU6623 is determined by this control signal from MPU. The control information includes register selection signals (RS), Set CG RAM address signals (AC) and data bus signals (DATA).

| INSTRUCTION                         |    |    |     |     | сo    | DDE  |              |               |       |                                                                                                                           | DESCRIPTION                                                                                                                                                                  | Execute Time  |  |

|-------------------------------------|----|----|-----|-----|-------|------|--------------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

|                                     | RS | AC | DB7 | D86 | DB5   | DB4  | DB3          | DB2           | DB1   | DB0                                                                                                                       |                                                                                                                                                                              | (fosc=153kHz) |  |

| Maker Testing                       | 0  | 0  | 0   | 0   | 0     | 0    | 0            | 0             | 0     | 0                                                                                                                         | All "0" code is using for maker testing.                                                                                                                                     | -             |  |

| Clear Display                       | 0  | 0  | 0   | 0   | 0     | 0    | 0            | 0             | 0     | 1                                                                                                                         | Display clear and sets RAM<br>address (00)н in AC.                                                                                                                           | 427.59us      |  |

| Return Home                         | 0  | 0  | 0   | 0   | 0     | 0    | 0 0 1 0      |               | 0     | Sets RAM address (09)⊢ in AC and<br>returns display being shifted original<br>position. RAM contents remain<br>unchanged. | Ous                                                                                                                                                                          |               |  |

| Entry Mode Set                      | 0  | 0  | 0   | 0   | 0     | 0    | 0 0 1 VD S p |               |       | s                                                                                                                         | Sets address move direction and<br>specifies shift of display are<br>performed in data write.<br>I/D=1:Increment,I/D=0:Decremen<br>S=1:Accompanies display shift             | Ous           |  |

| Display ON/OFF<br>Control           | 0  | 0  | 0   | 0   | 0     | 0    | 1            | D             | 0     | В                                                                                                                         | Sets of display On/Off(D) and blink of<br>cursor position character(B).                                                                                                      | Ous           |  |

| Address or Display<br>Shift         | 0  | 0  | o   | 0   | 0     | 1    | s/A          | S/A R/L 0 0 S |       | 0                                                                                                                         | Moves address & shifts display<br>without changing RAM contents<br>S/C=1 : Display shift<br>S/C=0 : address shift<br>R/L=1 : Shift to the right<br>R/L=0 : Shift to the left | Ous           |  |

| Set Static Port                     | 0  | 0  | ο   | o   | 1     | 0    |              |               | PO    | Sets Static port data.                                                                                                    | Ous                                                                                                                                                                          |               |  |

| Contrast control                    | 0  | o  | 0   | 1   | 0     | 0    | E            | .v.r.         | value | Ð                                                                                                                         | Sets data to Contrast Control<br>Register.                                                                                                                                   | Ous           |  |

| Set DD/MKRAM<br>Address             | ο  | 0  | 1   | ο   | 0     |      | a            | ddres         | is    |                                                                                                                           | Sets DD/MK RAM address. After this<br>instruction, the data is transferred to<br>RAM.                                                                                        | Ous           |  |

| Set CG RAM Address                  | 0  | 1  |     |     |       | add  | ddress ir    |               |       | Sets CG RAM address. After this<br>instruction, the data is transferred to<br>RAM.                                        | Ous                                                                                                                                                                          |               |  |

|                                     |    |    |     |     | Write | Data | Data(DD RAM) |               |       |                                                                                                                           |                                                                                                                                                                              |               |  |

| Write Data to CG<br>or DD or MK RAM | 1  | 0  |     |     |       |      | (C           | G RA          | M)    |                                                                                                                           | Writes data into RAM.                                                                                                                                                        | 41.38us       |  |

|                                     |    |    | 0   | 0   | 0     |      | (M           | K RA          | M)    |                                                                                                                           |                                                                                                                                                                              |               |  |

| *=Don't care                        |    |    |     | -   |       |      |              |               |       | -                                                                                                                         | enerator RAM, MK RAM : Icon display<br>time is also changed.                                                                                                                 | RAM           |  |

|  | Table 4. | Table of | of Instructions |

|--|----------|----------|-----------------|

|--|----------|----------|-----------------|

New Japan Radio Co., Ltd.

#### (4-1)Description of each instructions

(a)Maker Testing

|      | RS | AC | DB7 | DB <sub>6</sub> | DB₅ | DB4 | DB₃ | DB2 | DB1 | DBo |

|------|----|----|-----|-----------------|-----|-----|-----|-----|-----|-----|

| code | 0  | 0  | 0   | 0               | 0   | 0   | 0   | 0   | 0   | 0   |

All "0" code is using for device testing mode ( only for maker ).

Therefore, please avoid all "0" input or no meaning Enable signal input at data "0".

(Especially please check the output condition of Enable signal when the power turns on.)

#### (b)Clear Display

|      | RS | AC | DB7 | DB6 | DB₅ | DB4 | DB₃ | DB2 | DBı | DBo |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| code | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear display instruction is executed when the code "1" is written into DBo.

When this instruction is executed, the space code  $(20)_{H}$  is written into every DD RAM address, the DD RAM address (00)<sub>H</sub> is set into the address counter and entry mode is set to increment. The S of entry mode does not change.

Note: The character pattern for character code (20)<sub>H</sub> must be blank code in the user-defined character pattern (Custom font).

(c)Return Home

|      | RS | AC | DB7 | DB6 | DB₅ | DB4 | DB₃ | DB2 | DB1 | DBo |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| code | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   |

Return home instruction is executed when the code "1" is written into DB<sub>1</sub>. When this instruction is executed, the DD RAM address (00) $_{\text{H}}$  is set into the address counter. Display is returned its original position if shifted. The DD RAM contents do not change.

(d)Entry Mode Set

|      | RS | AC | DB7 | DB6 | DB₅ | DB₄ | DB₃ | DB2 | DB1 | <b>DB</b> o |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-------------|

| code | 0  | 0  | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S           |

Entry mode set instruction which sets the address moving direction and display shift On/Off, is executed when the code "1" is written into  $DB_2$  and the codes of (I/D) and (S) are written into  $DB_1(I/D)$  and  $DB_0(S)$ , as shown below.

(I/D) sets the address increment or decrement, and the (S) sets the whole display shift in the DD RAM writing.

| I/D | Function                                                                                                                                                                                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Address increment: The address of the DD RAM or MK RAM or CG RAM increment (+1) when the write.                                                                                                   |

| 0   | Address decrement: The address of the DD RAM or MK RAM or CG RAM decrement:( -1) when the write.                                                                                                  |

| s   | Func\tion                                                                                                                                                                                         |

| 1   | Whole display shift.<br>The shift direction is determined by I/D.: shift to the left at I/D=1 and shift to the<br>right at the I/D=0.<br>The display does not shift when writing into CG, MK RAM. |

|     |                                                                                                                                                                                                   |

#### (e)Display ON/OFF Control

|      | RS | AC | DB7 | DB6 | DB₅ | DB4 | DB₃ | DB2 | DB1 | DBo |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| code | 0  | 0  | 0   | 0   | 0   | 0   | 1   | D   | 0   | B   |

Display On/Off control instruction which controls the whole display On/Off and the addressed position character blink, is executed when the code "1" is written into  $DB_3$  and the codes of (D) and (B) are written into  $DB_2(D)$  and  $DB_0(B)$ , as shown below.

| D | Function                                                                                                                                            |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Display On.                                                                                                                                         |

| 0 | Display Off.I n this mode, the display data remains in the DD RAM so that it is retrieved immediately on the display when the D change to 1.        |

| В | Function                                                                                                                                            |

| 1 | The addressed position character is blinking. Blinking rate is 500ms at<br>f∞c=153kHz.<br>The cursor and the blink can be displayed simultaneously. |

| 0 | The character does not blink.                                                                                                                       |

|   |                                                                                                                                                     |

|   | Font 5 x 7 dotsAlternating displaysplay example(2)Blink display example                                                                             |

#### (f)Address/Display Shift

|      | RS | AC | DB7 | DB6 | DB₅ | DB4 | DB₃ | DB2 | DB1 | DBo |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| code | 0  | 0  | 0   | 0   | 0   | 1   | S/A | R/L | 0   | 0   |

The Cursor/Display shift instruction shifts the cursor position or display to the right or left without writing or reading display data. This function is used to correct or search the display.

The contents of address counter(AC) does not change by operation of the display shift only.

This instruction is executed when the code "1" is written into DB<sub>4</sub> and the codes of (S/A) and (R/L) are written into DB<sub>3</sub>(S/A) and DB<sub>2</sub>(R/L), as shown below.

| S/C | R/L | Function                                                            |

|-----|-----|---------------------------------------------------------------------|

| 0   | 0   | Shifts the address position to the left ((AC) is decremented by 1)  |

| 0   | 1   | Shifts the address position to the right ((AC) is incremented by 1) |

| 1   | 0   | Shifts the whole display to the left and the cursor follows it.     |

| 1   | 1   | Shifts the whole display to the right and the cursor follows it.    |

#### (g)Set Static Port

|      | RS | AC | DB7 | DB6 | DB₅ | DB4 | DB3 | DB2             | <b>DB</b> 1 | DB₀ |

|------|----|----|-----|-----|-----|-----|-----|-----------------|-------------|-----|

| code | 0  | 0  | 0   | 0   | 1   | 0   | P3  | P2 <sup>·</sup> | P1          | PO  |

It sets Static Output Port signal which can drive LED directly like as indicator. Initial status is "L".

New Japan Radio Co., Ltd.

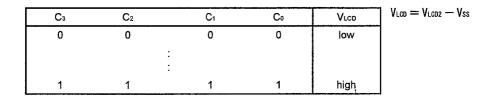

(h)Contrast Control

|      | RS | AC | DB7 | DB6 | DB₅ | DB4 | DB₃ | DB2 | DB1 | DB₀ | _ |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| code | 0  | 0  | 0   | 1   | 0   | 0   | C3  | C2  | C1  | Co  |   |

Contrast Control instruction which adjusts the contrast of the LCD, is executed when the code "1" is written into DB<sub>6</sub> and the codes of C<sub>3</sub> to C<sub>0</sub> are written into DB<sub>3</sub> to DB<sub>0</sub> as shown below.

The contrast of LCD can be adjusted one of 16 voltage-stages by setting this 4-bit register.

See (5-1) "how to adjust the Contrast of LCD".

Set the binary code "0000" when contrast adjustment is unused.

#### (i)Set DD/MK RAM Address

|      | RS | AC | DB7 | DB6 | DB₅ | DB4 | DB₃ | DB <sub>2</sub> | DB1 | DB₀ |

|------|----|----|-----|-----|-----|-----|-----|-----------------|-----|-----|

| code | 0  | 0  | 1   | 0   | 0   | A   | A   | A               | A   | Α.  |

The DD/MK RAM address set instruction is executed when the code "1" is written into DB<sub>7</sub> and the address is written into DB<sub>4</sub> to DB<sub>0</sub> as shown above.

\_ . . .

The address data (DB<sub>4</sub> to DB<sub>0</sub>) is written into the address counter (AC) by this instruction. After this instruction execution, the data writing is performed into the addressed DD/MK RAM.

The RAM includes DD RAM and MK RAM, and these RAMs are shared by address as shown below.

|        |   | RAM address   |

|--------|---|---------------|

| DD RAM | : | (00)н - (0Е)н |

| MK RAM | : | (10)н - (1Е)н |

(j)Set CG RAM Address

| _   | RS | AC | DB7 | DB6 | DB₅ | DB4 | DB₃        | DB2 | DB1 | DB₀ |

|-----|----|----|-----|-----|-----|-----|------------|-----|-----|-----|

| コード | 0  | 1  | A   | A   | A   | A   | <b>A</b> - | A   | A   | A   |

The CG RAM address set instruction is executed when the "H" level input to the AC terminal and the address is written into DB<sub>7</sub> to DB<sub>0</sub> as shown above.

The address data (DB7 to DB0) is written into the address counter (AC) by this instruction.

After this instruction execution, the data writing is performed into the addressed RAM.

The RAM includes CG RAM address as shown below.

RAM a - CG RAM : (00)

RAM address (00)H - (1F)H

New Japan Radio Co., Ltd.

τ

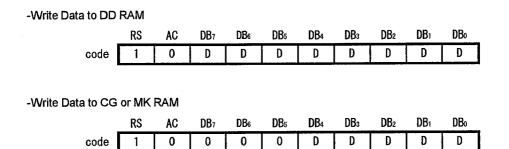

#### (k)Write Data to CG, DD or MK RAM

Write Data to RAM instruction is executed when the "H" level input to the RS terminal.

By the execution of this instruction, the binary 8-bit data ( $A_7$  to  $A_0$ ) are written into the DD RAM, and the binary 5bit data ( $A_4$  to  $A_0$ ) are written into the CG or MK RAM. The selection of RAM is determined by the previous instruction. After this instruction execution, the address increment(+1) or decrement(-1) is performed automatically according to the entry mode set. And the display shift is also executed according to the previous entry mode set.

#### (4-2)Initialization by instruction

If the power supply conditions for the correct operation of the internal reset circuits are not satisfied, the NJU6623 must be initialized by the instruction.

Note : When the Icon display function using, the system should be initialized by software initialization.

٤

## (5) LCD display

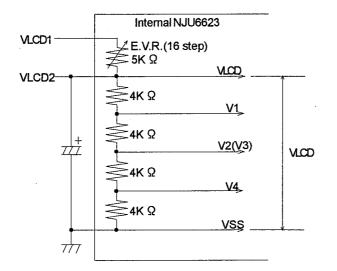

#### (5-1)Bleeder Resistance

Each LCD driving voltage ( $V_1$ ,  $V_2$ ,  $V_3$ ,  $V_4$ ) is LCD driving high voltage input to the VLCD1 terminal, generated by the E.V.R. and high impedance bleeder resistance.

The bleeder resistance is set 1/4 bias suitable for 1/8 duty ratio.

The capacitor connected between VLCD2 and Vss is needed for stabilizing VLCD. The determination of the each capacitance requires to operate with the LCD panel actually.

LCD Driving Voltage vs Duty Ratio

| Power  | Duty Ratio | 1/8        |

|--------|------------|------------|

| supply | Bias       | 1/4        |

|        |            | VLCD2- VSS |

VLCD is the maximum amplitude for LCD driving voltage.

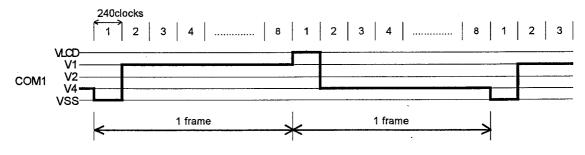

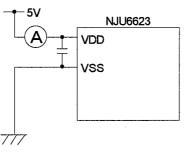

(5-2)Relation between oscillation frequency and LCD frame frequency

As the NJU6623 incorporate oscillation capacitor and resistor for CR oscillation, 153kHz oscillation is available without any external components.

The LCD frame frequency example mentioned below is based on 153kHz oscillation.(1clock = 6.54us)

1 frame = 6.54(us) x 240 x 8 = 12.55(ms) Frame frequency = 1 / 12.55(ms) = 79.68(Hz)

New Japan Radio Co., Ltd.

#### (6)Interface with MPU

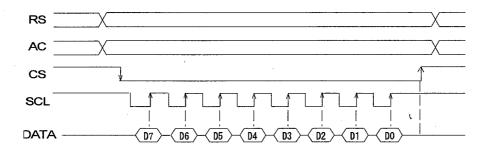

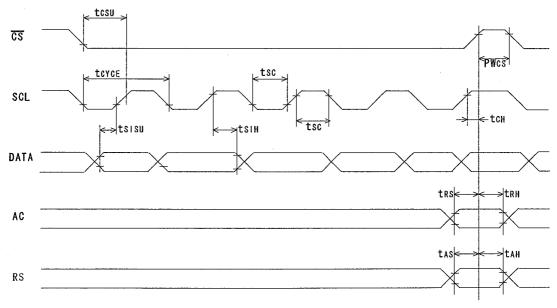

Serial interface circuit is activated when the chip select terminal (CS) goes to "L" level. The data input is MSB first like as the order of DB7, DB6 ..... DB0. The input data is entered into the shift register synchronized at the rise edge of the serial clock SCL. The latest 8bit data in the shift register converts to parallel data at the CS rise edge input. In case of entering over than 8-bit data, valid data is last 8-bit data. The time chart for the serial interface is shown below.

Note : The level ("L" or "H") of RS and R/W terminals should be set before CS terminal goes to "L" level.

# NJU6623

#### ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER             | SYMBOL | RATINGS          | UNIT | NOTE           |

|-----------------------|--------|------------------|------|----------------|

| Supply Voltage(1)     | VDD    | -0.3~+7.0        | V    |                |

| Supply Voltage(2)     | VLCD1  | VSS+10.5~VSS+0.3 | V    | VLCD1 Terminal |

| input Voltage         | Vin    | -0.3~VDD+0.3     | V    |                |

| Operating Temperature | Topr   | -30~+80          | °C   |                |

| Storage Temperature   | Tstg   | -55~+125         | °C   |                |

Note 1 : If the LSI are used on condition above the absolute maximum ratings, the LSI may be destroyed. Using the LSI within electrical characteristics is strongly recommended for normal operation. Use beyond the electric characteristics conditions will cause mal function and poor reliability.

Note 2 : Decoupling capacitor should be connected between VDD and Vss due to the stabilized operation for the Voltage converter.

Note 3 : All voltage values are specified as Vss = 0V

Note 4 : The relation : V<sub>DD</sub> > V<sub>SS</sub>, V<sub>DD</sub> > V<sub>SS</sub>≧V<sub>50UT</sub>, V<sub>SS</sub>≈0V must be maintained.

#### ■ ELECTRICAL CHARACTERISTICS

(VDD=4.5V~5.5V,Ta=-40°C~+80°C)

τ

| PAR                         | AMETER                | SYMBOL                                          | CONDITIONS                                         | MIN.   | TYP.   | MAX.   | UNIT | NOTE |

|-----------------------------|-----------------------|-------------------------------------------------|----------------------------------------------------|--------|--------|--------|------|------|

| Input Voltage               |                       | VIH                                             |                                                    | 0.8VDD | -      | VDD    | V    | 5    |

|                             |                       | VIL                                             |                                                    | VSS    | -      | 0.2VDD | V    | 5    |

| Output Voltage VOH VOL      |                       | VOH                                             | -IOH=2mA,VDD=5V                                    | 4.0    | -      | -      | V    | 6    |

|                             |                       | VOL                                             | IOL=2mA,VDD=5V                                     | -      | -      | 0.5    | V    | 6    |

| Driver On-resist.(COM) RCOM |                       | RCOM                                            | <u>+</u> Id=1uA(COM Terminal)<br>Vo=VLCD,VSS,V1,V4 | -      | -      | 40     | ĸΩ   | 8    |

| Driver On-resist.(SEG) RSEG |                       | <u>+</u> Id=1uA(SEG Terminal)<br>Vo=VLCD,VSS,V2 | -                                                  | -      | 40     | кΩ     | 8    |      |

| Input Leakage Current ILI   |                       | ILI                                             | VIN=0~VDD                                          | -1.0   | -      | 1.0    | uA   | 10   |

| Operating Current           |                       | IDD1                                            | VDD=5V fosc=153KHz<br>Ta=25°C, display             | -      | T.B.D. | ~      | uA   | 7    |

|                             |                       | IDD2                                            | VDD=5V, Ta=25°C<br>stand-by mode                   | -      | T.B.D. | -      | uA   | 7    |

| V1                          |                       | V1                                              | VLCD1-VSS=8V,Ta=25°C                               | 5.8    | 6.0    | 6.2    | V    |      |

| Bleeder<br>resistance       | V2                    | E.V.R. value "0000"                             | 3.8                                                | 4.0    | 4.2    | V      |      |      |

|                             | V4                    | COM/SEG terminal                                | 1.8                                                | 2.0    | 2.2    | V      |      |      |

| circuit                     | Bleeder<br>resistance | RB                                              | VLCD1-VSS=8V,Ta=25°C<br>E.V.R. value "0000"        | 11.2   | 16.0   | 20.8   | ĸΩ   |      |

| Oscillation Frequency fosc  |                       | VDD=5V,Ta=25°C                                  | 77                                                 | 153    | 229    | KHz    |      |      |

| LCD Display Voltage VLC     |                       | VLCD1                                           | VLCD1 Terminal,VSS=0V                              | VDD    | -      | 10.0   | V    | 9    |

| VCD1 Current ILCE           |                       | ILCD1                                           | VLCD1-VSS=8V                                       |        |        | 1      | mA   |      |

ł

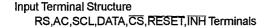

#### Note 5 : Input structure except LCD driver are shown below:

Note 6 : Apply to the Output and Input/Output Terminals.

Note 7 : Except Input/output current. If the input level is medium, current consumption will increase due to the penetration current. Therefore, the input level must be fixed to "H" or "L".

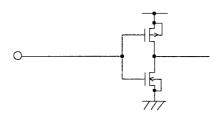

-Operating Current Measurement Circuit

- Note 8 : Rcom and Rcom are the resistance values between power supply terminals (Vss, VLCD2 or V1,V2,V4) and each common terminal (COM1 to COM7/COMMK) and supply voltage (Vss, VLCD2 or V1,V2,V4) and each segment terminal (SEG1 to SEG75) respectively, and measured when the current I<sub>d</sub> is flown on every common and segment terminals at a same time.

- Note 9 : Apply to the output voltage from each COM and SEG are less than ±0.15V against the LCD driving constant voltage (VDD, VSOUT) at no load condition.

- Note 10: Apply to the RS, AC, SCL, DATA, CS, RESET, INH.

# Bus timing characteristics

#### -Serial Interface Sequence

| PARAMETER                     | SYMBOL | MIN. | MAX. | CONDITION | UNIT |

|-------------------------------|--------|------|------|-----------|------|

| Serial clock cycle time       | tcyce  | 1    |      |           | us   |

| Serial clock width            | tsc    | 300  | -    | 1         | ns   |

| Chip select pulse width       | PWcs   | 100  | -    | <b>.</b>  | us   |

| Chip select set up time       | tcsu   | 300  | -    |           | ns   |

| Chip select hold time         | tсн    | 300  | -    |           | ns   |

| Serial input data set up time | tsisu  | 300  | -    | fig.1     | ns   |

| Serial input data hold time   | tsıн   | 300  | -    | -         | ns   |

| Register select set up time   | trs    | 300  | -    |           | ns   |

| Register select hold time     | trн    | 300  | -    |           | ns   |

| Address change set up time    | tas    | 300  | -    | 1         | ns   |

| Address change hold time      | tан    | 300  | -    | 1         | ns   |

# (VDD=4.5V~5.5V, VLCD1=Vss+8.0V, Ta=25°C)

#### Serial Interface

fig.1

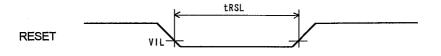

-The Input Condition when using the Hardware Reset Circuit

| PARAMETER                   | SYMBOL | CONDITION   | MIN | MAX | UNIT |

|-----------------------------|--------|-------------|-----|-----|------|

| Reset input "0" level width | trsl   | fosc=153kHz | 1.2 | -   | ms   |

-Power Supply Condition when using the internal initialization circuit (Ta=25°C)

| PARAMETER              | SYMBOL | CONDITION | MIN | MAX | UNIT |

|------------------------|--------|-----------|-----|-----|------|

| Power supply rise time | too    | -         | 0.1 | - 5 | ms 、 |

| Power supply OFF time  | toff   | -         | 1   | -   | ms   |

Since the internal initialization circuits will not operate normally unless the above conditions are met, in such a case initialize by instruction. (Refer to initialization by the instruction)

0.1ms ≦ trDD ≦ 5ms

tOFF ≧ 1ms

New Japan Radio Co., Ltd.

## LCD DRIVING WAVE FORM

# ■APPLICATION CIRCUITS

15-character 1-line Display Example

**MEMO**

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.